Actualmente, el procesador Arm más potente del planeta es el procesador A64FX de 48 núcleos de Fujitsu, que se construyó como un motor de computación fuertemente vectorizado para la supercomputadora «Fugaku» en RIKEN Lab en Japón. Nvidia se está preparando para enviar una CPU Arm «Grace» de 72 núcleos, a la que aún no se le ha dado un nombre de producto, pero el CG100 tiene sentido. Ambos se enfrentarán a la dura competencia del recién llegado con sede en India.

Existe una probabilidad distinta de cero de que el procesador Aum HPC diseñado por Centro de Desarrollo de Computación Avanzada (C-DAC) Puede superar tanto al A64FX como al Grace e incluso darle a Amazon su chip Graviton3 de 64 núcleos y los procesadores Ampere Computing Altra, Altra Max y AmpereOne por dinero en cargas de trabajo más generales.

Detalles del procesador Aum HPC mediodía esta semanaY no podríamos haber llegado en mejor momento porque nos cansamos un poco de escribir sobre IA y hay mucho silencio en TI, aunque esto fue una semana antes de la Conferencia Internacional de Supercomputación en Frankfurt. El procesador Aum HPC fue desarrollado bajo los auspicios de la Misión Nacional de Supercomputación del gobierno indio, y Sanjay Wandekar, Gerente Senior, HoD HPC Technologies Group en C-DAC, preparó la presentación que vimos.

La misión reúne al Instituto Indio de Ciencias, el Departamento de Ciencia y Tecnología, el Ministerio de Electrónica y Tecnología de la Información y C-DAC para lograr la independencia de HPC, desde el procesador hasta los sistemas completos y el software, hasta el Gobierno de la India. y las organizaciones que necesitan procesamiento de HPC, presumiblemente para los gigantes industriales indios que tampoco querrán depender de la subcontratación de silicio, sistemas y software para sus cargas de trabajo de HPC e IA. Este no es solo un esfuerzo técnico, sino también un esfuerzo de fabricación y diseño de centros de datos con un enfoque en la refrigeración líquida para las máquinas más potentes, suponemos, a exaescala. Este esfuerzo también incluye el desarrollo de aplicaciones de supercomputación de «interés nacional» y el desarrollo de la experiencia en programación y administración de sistemas necesaria para construir, mantener y ejecutar esas aplicaciones en producción.

Además de tener una cadena de suministro de piezas y sistemas de HPC que son inmunes a una posible importación a la India, el gobierno indio también desea saber, sin lugar a dudas, que no hay puertas traseras de seguridad en el hardware o el software que utiliza para implementar HPC. y aplicaciones de IA. Dado que India es una potencia nuclear que comparte frontera con China y está a tiro de piedra de Rusia, no es difícil entender por qué India adoptaría la arquitectura Arm y haría un procesador personalizado. Y no sería sorprendente si Pakistán, que también comparte frontera con India y tiene la misma cantidad de armas nucleares que India, también usaría un procesador dedicado. ¿Quizás estará basado en RISC-V?

El procesador Aum HPC no se limita al mercado de HPC, y podemos esperar que sus variantes también se utilicen en la IA y en los espacios generales de computación en la nube. Se espera que el chip esté disponible en 2024 e inicialmente se implementará en un sistema HPC experimental con más de 1 petaflop de rendimiento (se supone que este es el rendimiento máximo teórico). A continuación, el gobierno indio busca «prepararse con un diseño de sistema y subsistemas a exaescala» basados en la CPU Aum. (Por cierto, no creemos que «Aum» tenga nada que ver con la palabra «Arm», sino una ortografía alternativa de «Om», que es una romanización de una antigua palabra sánscrita que es un mantra sagrado en el hinduismo. fe.)

Para crear el procesador Aum, los técnicos de C-DAC estudiaron el procesador A64FX, el sistema Fugaku en RIKEN, así como el procesador Sparc64-VIIIfx anterior y la supercomputadora K vieron ampliamente lo que todos vemos en los datos de medición de HPCG. Mejor relación entre el ancho de banda de la memoria y las operaciones de punto flotante por segundo. De hecho, el sistema K tiene una relación byte/flop de 0,5 y ofrece un 5,2 % de rendimiento máximo de HPL en la prueba HPCG, en comparación con 0,38 byte/flop y un 3 % de la calificación máxima de Fugaku. Por lo tanto, el C-DAC decidió intentar que el ancho de banda de la memoria por tasa de giro sea superior a 0,5. Además, el C-DAC quería alejarse de la GPU y otros aceleradores y vectores relativamente pequeños que son fáciles de optimizar, además de proporcionar una combinación de memorias principales HBM y DDR y muchos carriles de E/S PCI-Express con CXL. apoyo a la coherencia.

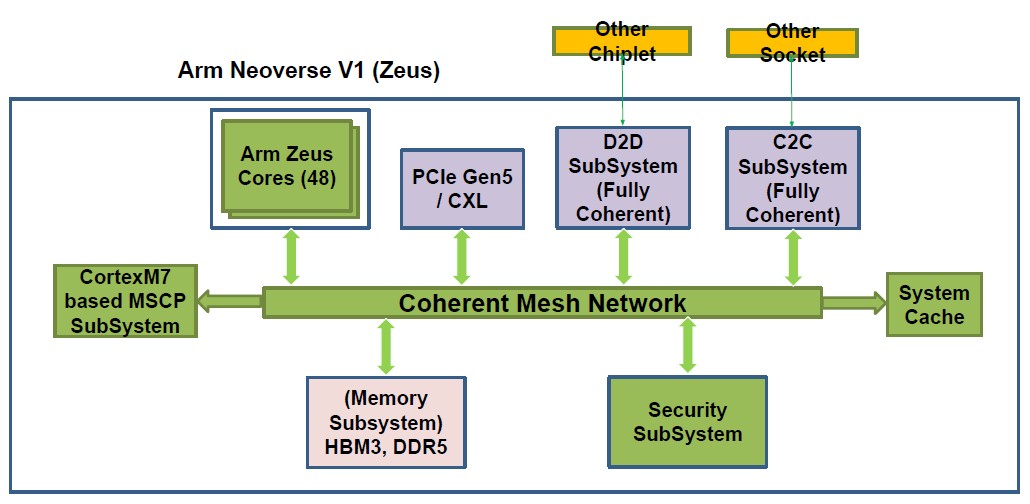

Así es como se ve el diagrama de bloques de una CPU Aum:

Como era de esperar, el C-DAC seleccionó los núcleos Neoverse V1 «Zeus» de Arm Holdings y puso 48 de ellos en un paquete. No sabemos si usa una arquitectura de chip, pero este chip A48Z, como también se le llama, parece un diseño roscado, como puede ver en el diagrama a continuación.

El subsistema de memoria del A48Z admite ocho canales de memoria DDR5 que funcionan a un máximo de 5,2 GHz y tiene un par de controladores de memoria HBM3 que funcionan a 6,4 GHz que se enrutan a 5,6 GHz en la versión inicial. La memoria HBM3 es de hasta 64 GB por paquete de chipset dual, que no es una gran cantidad de memoria, pero está mejorada con memoria DDR5. como el:

El paquete Aum incluiría un par de estos chips de 48 núcleos unidos mediante una conexión die-die (D2D), que es totalmente coherente.

Nvidia está haciendo un diseño de núcleo de cliente Arm V9 para la CPU Grace, mientras que C-DAC y AWS se apegan al núcleo Neoverse V1 de nivel Arm V8.4-A en sus diseños Graviton3/3E y Aum. Este paquete de CPU Aum de doble chip tiene un total de 96 núcleos, con 96 MB de caché L2 en esos núcleos y otro caché de todo el sistema de 96 MB compartido entre los núcleos y el caché entre la memoria DDR5, HBM3 y caché L2.

Además de la interconexión D2D, existe otra comunicación de chip a chip (C2C) basada en el protocolo CCIX creado por Xilinx y respaldado por Arm Holdings, que permitirá que varios paquetes se vinculen juntos a lo largo de las líneas de NUMA para una consistencia total de la memoria. . No está claro hasta dónde se puede llevar CCIX NUMA, pero se han revelado dos sockets como mínimo, pero es probable que cuatro sockets admitan grandes huellas de servidor de memoria en algún momento, y ocho sockets son totalmente posibles si la interconexión C2C tiene suficientes carriles. Cada chip Aum tiene 64 carriles de conectividad PCI-Express 5.0, para un total de 128 carriles, y creemos que 64 de esos carriles se utilizan para proporcionar enlaces NUMA basados en el protocolo CCIX entre los zócalos Aum, tal como lo hace AMD con su Procesadores Epyc que utilizan el protocolo Infinity Fabric.

El C-DAC dice que un nodo Aum, que presumiblemente tiene dos CPU, proporcionará alrededor de 10 teraflops de pico de cómputo. Un servidor Aum de dos sockets tendrá suficiente ancho de banda para agregar cuatro aceleradores de GPU.

No sabemos si la red cohesiva que conecta los núcleos a los controladores en el chip A48Z tiene licencia de Arm Holdings o local. Puede tener licencia de Arm Holdings.

Parece que el procesador Aum tendrá una velocidad de reloj base de 3 GHz, con un impulso turbo de más de 3,5 GHz. Con 16 canales de memoria DDR5 que proporcionan un ancho de banda de 332,8 GB/s y 64 GB de memoria HBM3 (2 grupos de 16 GB por chip A48Z) que proporcionan 2,87 Tb/s, el paquete Aum ofrecerá más de 4,6 Taflops por socket y 3 Tb/s de ancho de banda de memoria total , para un flop de 0,7 bytes por proceso.

Todo ello en un punto de diseño térmico de 300 vatios. El procesador A64FX de Fugaku, la memoria HBM2 y la interconexión Tofu D pesan alrededor de 170 vatios. Este sistema Fugaku presenta medidas superiores de eficiencia energética.

Aquí hay un gráfico interesante que Wandhekar puso sobre la mesa:

Habíamos agregado Graviton2 y Graviton3, así como el próximo procesador Ampere Computing AmpereOne, que muy probablemente supera a todos estos chips en muchas métricas. Cuando sepamos más, le construiremos una tabla de este tipo.

«Food ninja. Freelance pop culture fanatic. Wannabe zombie maven. Twitter aficionado.»

More Stories

La red social Butterflies AI añade una función que te convierte en un personaje de inteligencia artificial

Edición del vigésimo aniversario de Hautlence HLXX: redefiniendo el tiempo con minutos que retroceden y horas saltantes

Un marco para resolver ecuaciones diferenciales parciales equivalentes puede guiar el procesamiento y la ingeniería de gráficos por computadora