Escrito por Sapana Maurya, Sunil Chaudhary (eInfochips)

1. Introducción

Para diseños de nodos de baja tecnología, se recomienda utilizar bibliotecas de temporización CCS (fuente de corriente combinada) porque las bibliotecas NLDM (modelo de retardo no lineal) no pueden diseñar una alta resistencia a la interconexión, la propagación del ruido y los efectos físicos como el efecto Miller. Este cálculo impreciso del retraso de la celda requiere el uso de bibliotecas de temporización CCS.

Las bibliotecas de temporización CCS tienen tamaños de archivo más grandes que las bibliotecas NLDM, lo que resulta en tiempos de ejecución más prolongados y un mayor uso de memoria durante la fase de ejecución real.

Sin embargo, establecer una mejor correlación entre la aprobación y la simulación de circuitos (HSPICE) dentro de un rango de precisión aceptable es fundamental para garantizar la calidad del diseño.

Como resultado, surge la pregunta sobre la correlación de tiempos debido a los diferentes modelos de tiempos utilizados durante las fases de ejecución y firma.

Para abordar este problema, se requiere una mayor precisión debido al menor margen tecnológico permitido. Verificar la precisión de las bibliotecas de tiempos CCS en la herramienta de pago se vuelve esencial para obtener resultados precisos durante la fase de ejecución real.

Este artículo presenta el análisis de correlación temporal entre la herramienta de pago y HSPICE para el diseño de un nodo tecnológico de 5 nm. Exploraremos varios tipos de análisis de correlación de tiempos y determinaremos la precisión de las bibliotecas en función de los resultados de la correlación.

2- Flujo de enlace de tiempo

Durante el flujo de diseño, después de caracterizar la biblioteca, es necesario realizar la validación de la biblioteca antes de comenzar la correlación de tiempos. La validación es útil para confirmar la calidad temporal de los datos CCS y de ruido en las bibliotecas.

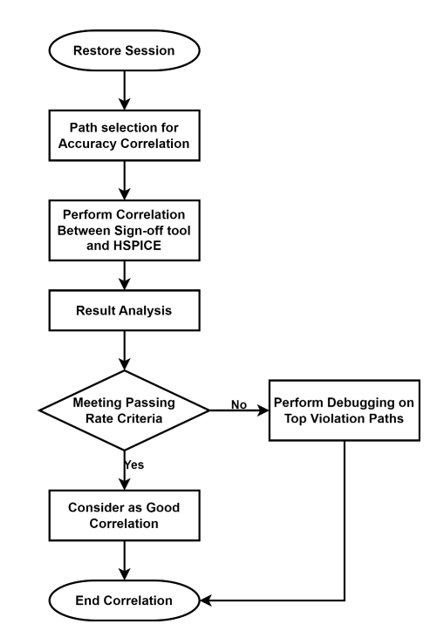

Para realizar esta validación, puede utilizar la herramienta EDA proporcionada por Synopsys Library Compiler. Después de la validación de la biblioteca, se puede realizar una correlación de tiempos en estas bibliotecas validadas. El flujo de correlación temporal se muestra en la siguiente figura:

apariencia. Sincronización del enlace de flujo

2-1- Estándares de correlación de precisión

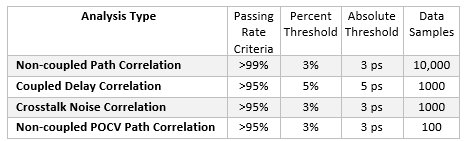

La siguiente tabla muestra los criterios considerados para la correlación de precisión:

Tabla 1. Criterios de correlación de precisión

2-2- Elija la ruta para el enlace de precisión

Elegir rutas para el enlace no emparejado:

Esta sección proporciona pautas para especificar rutas para la correlación de resolución. Primero, seleccione un número fijo de rutas al azar, luego filtre las rutas según las condiciones/criterios especificados:

- Las rutas en el bucle pueden causar problemas en la simulación y deben eliminarse de la selección.

- El punto final no debe ser un pin asíncrono.

- El punto final y el punto inicial no deben ser la misma celda.

- No debería haber ningún valor de estado en el pin de registro D.

Elija pines para doble enlace

- Debemos tener un conjunto de pines de entrada antes de que podamos comenzar a calcular el retraso o el ruido asociado con el procedimiento de correlación de precisión.

- Recoja redes que tengan grandes deltas superpuestos o crestas superpuestas en el diseño.

- Por ejemplo, la herramienta Cerrar sesión tiene un comando para desconectar redes con una gran superposición delta en rutas de configuración con un intervalo inferior a 0.

Elegir rutas para un enlace POCV:

Para la correlación POCV, debemos elegir rutas con buenos resultados de correlación de rutas no apareadas. La unión débil no apareada puede afectar los resultados de correlación de POCV.

Los criterios para seleccionar estos caminos son:

- El error del enlace HSPICE debe estar dentro del límite permitido.

- Los caminos deben tener un número razonable de etapas, ni demasiado cortas ni demasiado largas en términos de profundidad lógica. Los caminos cortos dificultan lograr una correlación razonable, mientras que los caminos largos conducen a tiempos de ejecución de simulación más largos.

- Todos los caminos deben tener una variación razonable, con un pequeño porcentaje de POCV a llegadas a caminos desocupados.

2-3- Tipos de correlación de precisión

2-3-1- Enlace de ruta no emparejado:

La correlación de rutas de efectos acoplados o desacoplados se puede realizar después de seleccionar un conjunto de rutas para una correlación de precisión. Los datos de las simulaciones de HSPICE y los datos de los informes de las herramientas de aprobación deben compararse para correlacionar los dos conjuntos de datos.

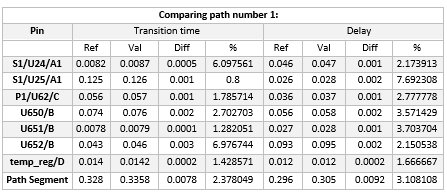

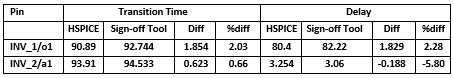

Un ejemplo de esto se da a continuación:

Tabla 2. Correlación de ruta no apareada

Enlace de precisión de la ruta del reloj de captura:

- Del mismo modo, necesita un CRPR de punto común y un pin de reloj de punto final para un enlace de resolución de ruta de reloj desacoplado. Al igual que con los datos no emparejados, necesitamos vincular los datos. La única diferencia aquí es que la ruta captura la ruta del reloj en lugar de la ruta de datos.

2-3-2- Enlace de interferencia/retardo acoplado:

- La interferencia/retraso acoplado ocurre cuando las redes del agresor y la víctima cambian juntas.

- El dúplex se realiza en función de los valores de subida y bajada, y el retraso se mide desde las entradas del controlador hasta las entradas del receptor.

2-3-3- Correlación del ruido del habla:

- Ruido de diafonía Ocurre cuando la red del agresor pasa una señal fija y las redes de la víctima cambian.

- Podemos utilizar los criterios anteriores para seleccionar picos para la correlación de ruido.

- Realice una correlación de ruido de diafonía basada en la altura y la resolución del área en las cuadrículas correspondientes. Debemos tener una lista de pines de entrada a través de los cuales se puede realizar la correlación de precisión.

2-3-4- Enlace de ruta POCV:

- Antes de comenzar a vincular una ruta POCV, debe tener una lista de rutas seleccionadas para la resolución del enlace. Siga las pautas y recomendaciones de la sección Selección de una ruta para una correlación de precisión para seleccionar un buen conjunto de rutas para una correlación POCV.

- La relación entre la llegada del trayecto (con variación) y la llegada del trayecto nominal (sin variación) debe ser inferior a 2,0. Después de obtener la lista de rutas definidas, puede realizar una asociación de ruta POCV.

2-4- Corrección de los caminos violadores:

- Análisis de una sola etapa = entrada del conductor a salida del conductor

Informe de correlación para una etapa.

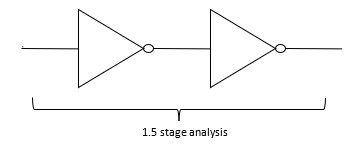

- Análisis de una etapa y media = entrada del controlador a salida del receptor

1.5 Etapa del informe de correlación

- Identifique las fases que más causan errores de correlación en la ruta de los informes.

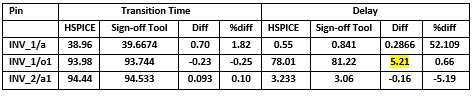

- Para corregir una sola ruta, realice análisis de 1 fase y 1,5 fases utilizando también el modelo CCS y NLDM y observe los resultados, verificando las diferencias en ambos modelos de sincronización.

- En el ejemplo anterior, podemos ver en el informe de correlación de fase 1.5, la diferencia de retardo es 5.21 ps, lo cual está más allá del límite de estándares como se menciona en la tabla de estándares de correlación de precisión -1 anterior, por lo tanto, debemos realizar la caracterización de celda en el inversor INV_1. .

- Si falla el 10% del total de indicadores, significa que la celda tiene un problema de caracterización y se debe presentar un informe adicional por todas esas celdas.

3 – Conclusión

Las bibliotecas de temporización CCS son más precisas que las bibliotecas de temporización NLDM y, para diseños de nodos de menor tecnología, se recomienda verificar la precisión de las bibliotecas de temporización CCS en la herramienta de pago. Por lo tanto, para verificar esto, se realiza un análisis de correlación de tiempos entre la herramienta de pago y HSPICE.

4- Los autores

Sapana Maurya

Sapana Maurya trabaja como ingeniera de diseño físico en eInfochips. Tiene una Maestría en Ingeniería en Procesamiento de Señales y Tecnología VLSI de Vishwakarma Government Engineering College, Ahmedabad, India. Tiene más de 1 año de experiencia en diseño de ASIC, incluida la actividad, el lugar y la ruta de certificación EDA, y el análisis STA en nodos tecnológicos posteriores.

Sunil Chaudhary

Sunil Chaudhary trabaja como ingeniero de diseño físico en eInfochips. Tiene una Maestría en Ingeniería en Procesamiento de Señales y Tecnología VLSI de la Vishwakarma Government Engineering College, Ahmedabad, India. Tiene más de 2 años de experiencia en diseño de ASIC, incluida la actividad, el lugar y la ruta de certificación EDA, y el análisis STA en nodos tecnológicos posteriores.

Si desea descargar una copia de este documento técnico, haga clic aquí

«Food ninja. Freelance pop culture fanatic. Wannabe zombie maven. Twitter aficionado.»

More Stories

La red social Butterflies AI añade una función que te convierte en un personaje de inteligencia artificial

Edición del vigésimo aniversario de Hautlence HLXX: redefiniendo el tiempo con minutos que retroceden y horas saltantes

Un marco para resolver ecuaciones diferenciales parciales equivalentes puede guiar el procesamiento y la ingeniería de gráficos por computadora